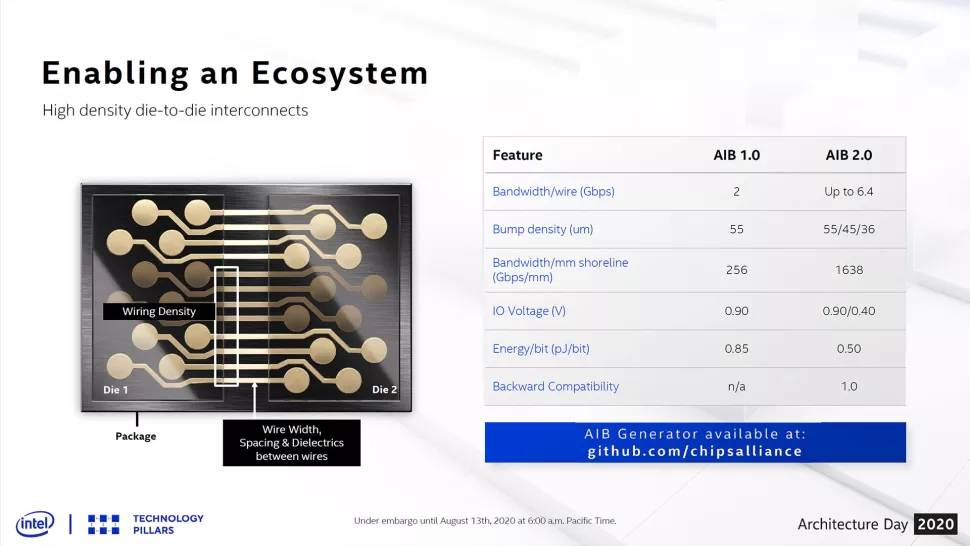

อินเทอร์เฟซ AIB (Advanced Interface Bus) มาตรฐานที่เป็นกุญแจสำคัญในการปลดล็อกระดับความร่วมมือและการบูรณาการระหว่างพันธมิตรจำนวนมาก อินเทลได้ทำงานเพื่อพัฒนามาตรฐานมาก่อนหน้านี้แล้ว โดยให้การสนับสนุนเป็นพันธมิตร

กับโอเพ่นซอร์ส CHIPS โดยไม่ต้องใช้ค่าลิขสิทธิ์หรือใบอนุญาต ส่งผลให้บริษัทอื่นสามารถพัฒนาชิปเล็ตที่เข้ากันได้กับทั้งชิปเล็ตของอินเทลและของบริษัทอื่นด้วย Intel กล่าวว่าความคิดริเริ่มนี้ได้นำไปใชักับ 10 ชิ้นส่วน(Tile)ที่ใช้ AIB จากหลายบริษัท

อยู่ในระหว่างการผลิตหรืออยู่ในขั้นตอนการเร่งพัฒนา ผู้ผลิตชิปยังกล่าวว่า มีอีก 10 ชิ้นส่วนที่บริษัทสตาร์ทอัพและมหาวิทยาลัยที่กำลังอยู่ระหว่างการพัฒนา ชิ้นส่วนเหล่านี้ประกอบไปด้วยฟังก์ชันต่างๆ เช่น ตัวรับส่งสัญญาณความเร็วสูง ตัวแปลง

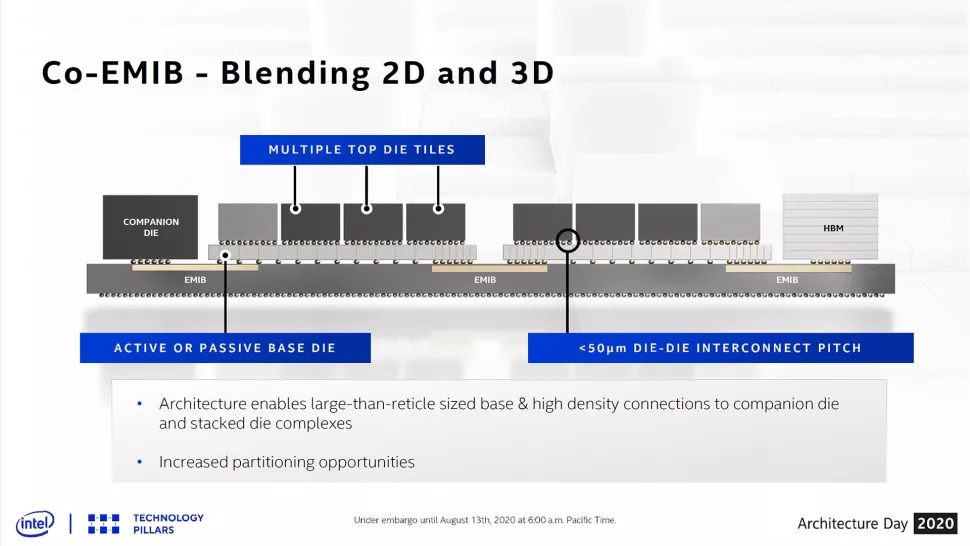

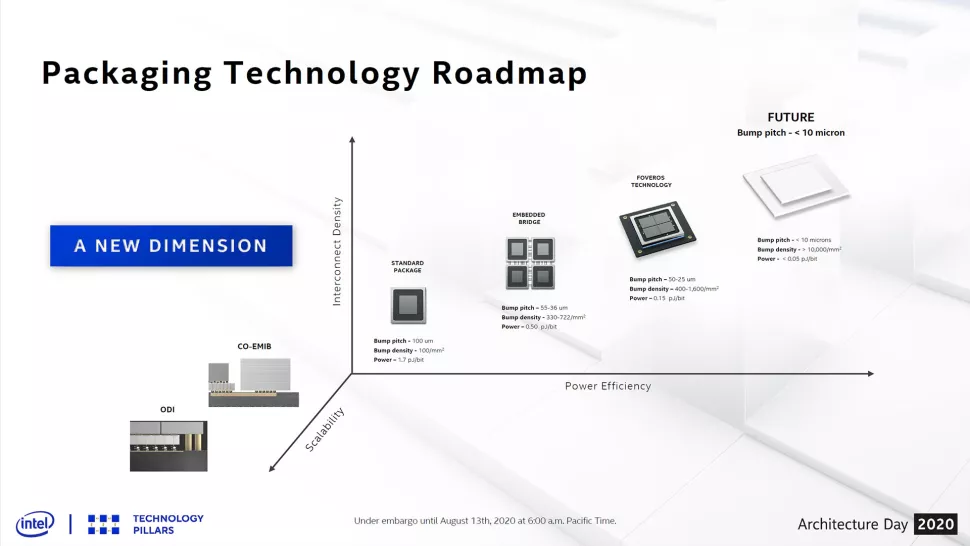

ข้อมูล ซิลิคอนโฟโตนิกส์และตัวเร่งการเรียนรู้ของเครื่อง สำหรับ FPGAของอินเทลใช้จำนวนชิปเล็ตมากอยู่แล้ว เนื่องจากมักทำหน้าที่เป็นตัวขับเคลื่อนหลักสำหรับเทคโนโลยีบรรจุภัณฑ์ขั้นสูงของอินเทล อันที่จริง FPGA รุ่นต่อไปของอิเทล จะเป็นอุปกรณ์

ขนาดใหญ่เครื่องแรกที่ใช้บรรจุภัณฑ์แบบ Foveros 3D

Comment