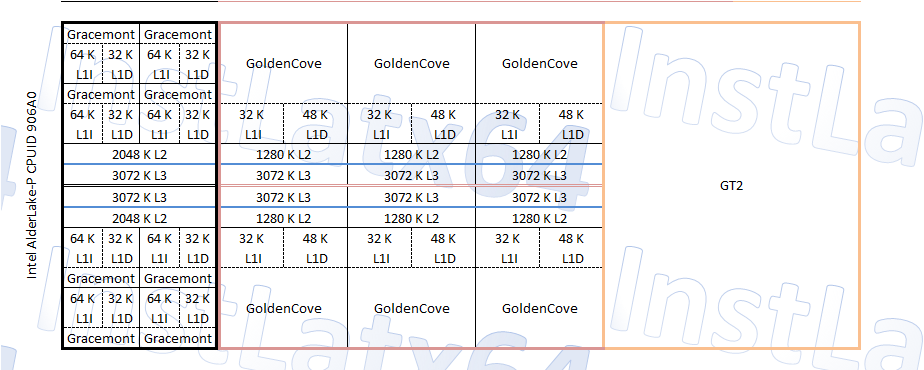

-Intel Core i9 K-Series (8 Golden + 8 Grace) = 16 Cores / 24 Threads

-Intel Core i7 K-Series (8 Golden + 4 Grace) = 12 Cores / 20 Threads

-Intel Core i5 K-Series (6 Golden + 4 Grace) = 10 Cores / 16 Threads

-Intel Core i9 A-Series (8 Golden + 8 Grace) = 16 Cores / 24 Threads

-Intel Core i7 A-Series (8 Golden + 4 Grace) = 12 Cores / 20 Threads

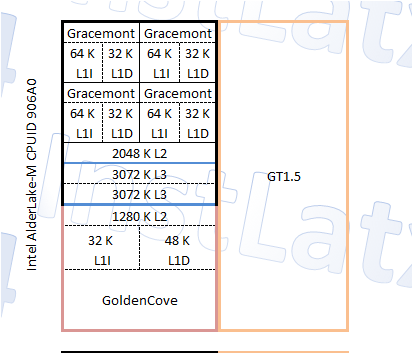

-Intel Core i5 A-Series (6 Golden + 0 Grace) = 6 Cores / 12 Threads

-Intel Core i3 A-Series (4 Golden + 0 Grace) = 4 Cores / 8 Threads

-Intel Core i7 K-Series (8 Golden + 4 Grace) = 12 Cores / 20 Threads

-Intel Core i5 K-Series (6 Golden + 4 Grace) = 10 Cores / 16 Threads

-Intel Core i9 A-Series (8 Golden + 8 Grace) = 16 Cores / 24 Threads

-Intel Core i7 A-Series (8 Golden + 4 Grace) = 12 Cores / 20 Threads

-Intel Core i5 A-Series (6 Golden + 0 Grace) = 6 Cores / 12 Threads

-Intel Core i3 A-Series (4 Golden + 0 Grace) = 4 Cores / 8 Threads

Comment