กลายเป็นข่าวฮือฮาเมื่อ AMD ได้จดสิทธิบัตรเทคโนโลยี Hybrid CPU ในแบบของตัวเอง ถือว่าน่าสนใจมากครับว่าทิศทางการพัฒนาของ AMD จะไปในทางไหน

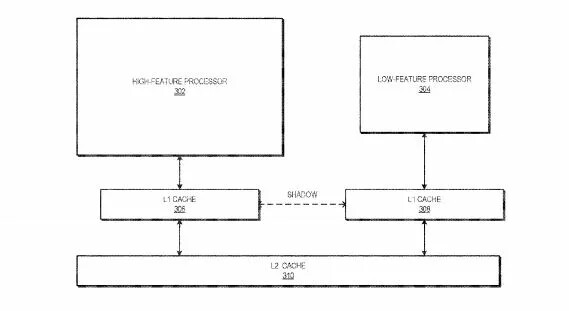

เทคโนโลยี Hybrid CPU ของ AMD หลักการคร่าวๆก็คือจะมี CPU 2 ระดับ (Low-Feature และ High-Feature) ทำงานร่วมกัน ส่งต่อ workload ให้กันและกันได้ ซึ่งก็คล้ายๆกับ big.LITTLE ของ Arm นั่นเอง (รวมถึง Lakefield และ Alder Lake ของอินเทลด้วย) เป้าหมายสำคัญคือทำให้ชิพกินไฟน้อยที่สุดเมื่ออุปกรณ์ทำงานเบาๆหรือ Standby อยู่ ผลก็คือประหยัดแบตฯ

โดยเทคนิค big.LITTLE บน CPU Arm (รุ่น Cortex ทั้งหลาย) จะประกอบด้วย big Core ซึ่งมีสมรรถนะสูงแต่กินไฟมาก กับ LITTLE Core ที่มีคุณสมบัติตรงกันข้าม ซึ่งหลักการทำงานแบ่งเป็น 3 แบบดังนี้ (ดูรูปเพื่อประกอบความเข้าใจ)

1. Clustered switching

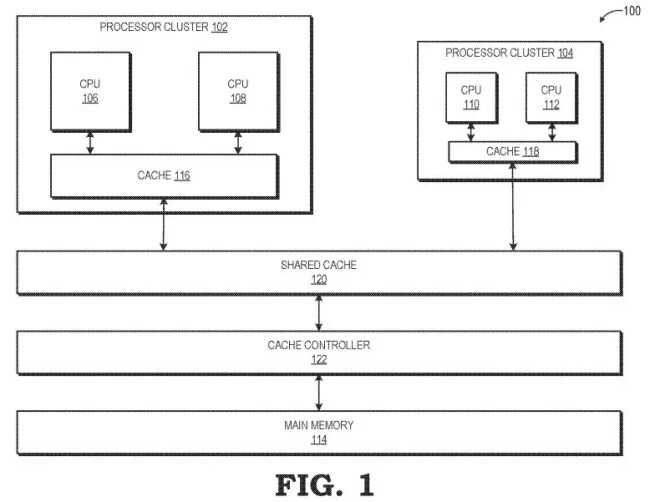

เป็นแบบง่ายที่สุด คือ แบ่งแยกเป็น 2 ฝั่ง big และ LITTLE ชัดเจนและใช้งานทีละฝั่งไปเลย เพราะ OS จะมองเห็นทีละ 1 Cluster เท่านั้น เมื่อภาระของ CPU เปลี่ยนไป ระบบก็จะส่งต่อการประมวลผลทั้งหมดไปให้อีก Cluster นึง โดยข้อมูลจะถูกโอนย้ายผ่านแคช L2 ที่ใช้ร่วมกัน แล้วระบบก็จะปิดไฟเลี้ยง Cluster เดิมทั้งหมด รูปแบบนี้เป็นรุ่นแรกๆซึ่งไม่มีความยืดหยุ่น เพราะทั้งระบบจะต้องเลือกระหว่าง big หรือ LITTLE Core อย่างใดอย่างหนึ่งในเวลาเดียวกันเท่านั้น

รูป big.LITTLE แบบ clustered switching

2. In-kernel switcher (CPU migration)

การสลับ CPU ในแบบนี้จะจับคู่ big กับ LITTLE Core คู่ใครคู่มัน โดย OS จะมองเห็นแต่ละคู่เป็น 1 Virtual Core เท่านั้น ซึ่งหลังฉากมันจะสลับใช้งานทีละคอร์ เมื่อภาระงานสูงก็จะใช้ big Core และเมื่อภาระงานน้อยจะก็ใช้ LITTLE Core ในการส่งต่องาน ระบบจะปลุก (จ่ายไฟให้) Core ที่จะมาแทน และส่งต่อข้อมูลสถานะการประมวลผลไปให้ จากนั้นก็ปิด Core เดิม และประมวลผลต่อใน Core ใหม่ รูปแบบนี้ถือว่าก้าวหน้าและยืดหยุ่นกว่าแบบแรก เพราะแต่ละคู่จะเลือก Core อย่างอิศระ ทั้งระบบจึงอาจมีทั้ง big และ LITTLE Core ทำงานอยู่ในเวลาเดียวกัน

รูป big.LITTLE แบบ in-kernel switcher

3. Heterogeneous multi-processing (global task scheduling)

รูปแบบนี้ก้าวหน้าและยืดหยุ่นมากที่สุด เพราะทุก Core ในระบบไม่ว่าจะ big หรือ LITTLE จะเปิดหรือปิดใช้งานอย่างอิศระในเวลาเดียวกัน โดย Thread ไหนที่มีลำดับความสำคัญสูงหรือต้องคำนวณหนักจะส่งไปให้ big Core ส่วน Thread ที่ไม่สำคัญหรือคำนวณไม่หนักมาก LITTLE Core จะรับหน้าที่เอง

รูป big.LITTLE แบบ heterogeneous multi-processing

สำหรับ Hybrid CPU ของ AMD เท่าที่อ่านและวิเคราะห์ดู มันคล้ายกับ big.LITTLE ในแบบที่ 2 (In-kernel switcher) ครับ ซึ่งผมมองว่าเป็นตัวเลือกที่เหมาะสม เพราะมีความยืดหยุ่นพอสมควร แม้จะไม่ทรงพลังเท่าแบบที่ 3 แต่มันง่ายต่อการใช้งานจริงมากกว่า เพราะฝั่ง OS หรือ Software ไม่ต้องรองรับอะไรเพิ่มเติม เนื่องจาก OS มองเห็นแต่ละคู่ (High กับ Low-Feature) เป็น Core เดียวอยู่แล้ว เบื้องหลังเดี๋ยว CPU จัดสรรเอง อย่างไรก็ตามนี่เป็นเพียงการคาดเดาของผมเท่านั้น ผมยังไม่อ่านรายละเอียดทั้งหมด เพื่อนคนไหนมีความคิดเห็นยังไงก็มาพูดคุยแลกเปลี่ยนกันได้ครับ

อ้างอิง

https://www.guru3d.com/news-story/am...-a-patent.html

https://en.wikipedia.org/wiki/ARM_big.LITTLE

เทคโนโลยี Hybrid CPU ของ AMD หลักการคร่าวๆก็คือจะมี CPU 2 ระดับ (Low-Feature และ High-Feature) ทำงานร่วมกัน ส่งต่อ workload ให้กันและกันได้ ซึ่งก็คล้ายๆกับ big.LITTLE ของ Arm นั่นเอง (รวมถึง Lakefield และ Alder Lake ของอินเทลด้วย) เป้าหมายสำคัญคือทำให้ชิพกินไฟน้อยที่สุดเมื่ออุปกรณ์ทำงานเบาๆหรือ Standby อยู่ ผลก็คือประหยัดแบตฯ

โดยเทคนิค big.LITTLE บน CPU Arm (รุ่น Cortex ทั้งหลาย) จะประกอบด้วย big Core ซึ่งมีสมรรถนะสูงแต่กินไฟมาก กับ LITTLE Core ที่มีคุณสมบัติตรงกันข้าม ซึ่งหลักการทำงานแบ่งเป็น 3 แบบดังนี้ (ดูรูปเพื่อประกอบความเข้าใจ)

1. Clustered switching

เป็นแบบง่ายที่สุด คือ แบ่งแยกเป็น 2 ฝั่ง big และ LITTLE ชัดเจนและใช้งานทีละฝั่งไปเลย เพราะ OS จะมองเห็นทีละ 1 Cluster เท่านั้น เมื่อภาระของ CPU เปลี่ยนไป ระบบก็จะส่งต่อการประมวลผลทั้งหมดไปให้อีก Cluster นึง โดยข้อมูลจะถูกโอนย้ายผ่านแคช L2 ที่ใช้ร่วมกัน แล้วระบบก็จะปิดไฟเลี้ยง Cluster เดิมทั้งหมด รูปแบบนี้เป็นรุ่นแรกๆซึ่งไม่มีความยืดหยุ่น เพราะทั้งระบบจะต้องเลือกระหว่าง big หรือ LITTLE Core อย่างใดอย่างหนึ่งในเวลาเดียวกันเท่านั้น

รูป big.LITTLE แบบ clustered switching

2. In-kernel switcher (CPU migration)

การสลับ CPU ในแบบนี้จะจับคู่ big กับ LITTLE Core คู่ใครคู่มัน โดย OS จะมองเห็นแต่ละคู่เป็น 1 Virtual Core เท่านั้น ซึ่งหลังฉากมันจะสลับใช้งานทีละคอร์ เมื่อภาระงานสูงก็จะใช้ big Core และเมื่อภาระงานน้อยจะก็ใช้ LITTLE Core ในการส่งต่องาน ระบบจะปลุก (จ่ายไฟให้) Core ที่จะมาแทน และส่งต่อข้อมูลสถานะการประมวลผลไปให้ จากนั้นก็ปิด Core เดิม และประมวลผลต่อใน Core ใหม่ รูปแบบนี้ถือว่าก้าวหน้าและยืดหยุ่นกว่าแบบแรก เพราะแต่ละคู่จะเลือก Core อย่างอิศระ ทั้งระบบจึงอาจมีทั้ง big และ LITTLE Core ทำงานอยู่ในเวลาเดียวกัน

รูป big.LITTLE แบบ in-kernel switcher

3. Heterogeneous multi-processing (global task scheduling)

รูปแบบนี้ก้าวหน้าและยืดหยุ่นมากที่สุด เพราะทุก Core ในระบบไม่ว่าจะ big หรือ LITTLE จะเปิดหรือปิดใช้งานอย่างอิศระในเวลาเดียวกัน โดย Thread ไหนที่มีลำดับความสำคัญสูงหรือต้องคำนวณหนักจะส่งไปให้ big Core ส่วน Thread ที่ไม่สำคัญหรือคำนวณไม่หนักมาก LITTLE Core จะรับหน้าที่เอง

รูป big.LITTLE แบบ heterogeneous multi-processing

สำหรับ Hybrid CPU ของ AMD เท่าที่อ่านและวิเคราะห์ดู มันคล้ายกับ big.LITTLE ในแบบที่ 2 (In-kernel switcher) ครับ ซึ่งผมมองว่าเป็นตัวเลือกที่เหมาะสม เพราะมีความยืดหยุ่นพอสมควร แม้จะไม่ทรงพลังเท่าแบบที่ 3 แต่มันง่ายต่อการใช้งานจริงมากกว่า เพราะฝั่ง OS หรือ Software ไม่ต้องรองรับอะไรเพิ่มเติม เนื่องจาก OS มองเห็นแต่ละคู่ (High กับ Low-Feature) เป็น Core เดียวอยู่แล้ว เบื้องหลังเดี๋ยว CPU จัดสรรเอง อย่างไรก็ตามนี่เป็นเพียงการคาดเดาของผมเท่านั้น ผมยังไม่อ่านรายละเอียดทั้งหมด เพื่อนคนไหนมีความคิดเห็นยังไงก็มาพูดคุยแลกเปลี่ยนกันได้ครับ

อ้างอิง

https://www.guru3d.com/news-story/am...-a-patent.html

https://en.wikipedia.org/wiki/ARM_big.LITTLE

Comment